[发布时间]:2010年7月27日

[来源]:电子变压器资讯网

[点击率]:43801

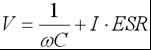

对于ESR来说也是同样的,如果要更有效的对一个电源分布系统去耦,使用一个ESR尽可能小的电容会更有效果。为了便于说明,我们将实际的寄生电阻ESR写到公式(2)中:

(7)

(7)

这就意味着不管电容怎样增大,ESR都会产生电压降。在实际应用中,我们必须增加电容值并减小ESR以尽可能的减小电源分布系统的纹波噪声。同时,公式(2)和(7)表述了在高频的情况下,大电容不会对减少电压降有太大的作用。反而,公式(6)表明减小感抗比较增大电容有更明显的效果。

2去耦电容的选择

在低频范围(几十MHz),电容呈现容性,高电容(并且有着低的ESR)将会有助于减少纹波噪声。添加去耦电容可以在一个特定的频率内减小纹波电压:

投稿箱:

电子变压器、电感器、磁性材料等磁电元件相关的行业、企业新闻稿件需要发表,或进行资讯合作,欢迎联系本网编辑部QQ:

, 邮箱:

info%ett-cn.com (%替换成@)。