[发布时间]:2010年7月27日

[来源]:电子变压器资讯网

[点击率]:42824

(2)

(2)

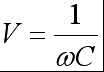

公式(2)说明了吸取电流导致的电压降V。正如大多数的CMOS电路,IC只有在晶体管开关时才会汲取电流。这意味着当IC开关时就汲取电流,会产生一个电压降而造成电源分布系统的电源纹波噪声。进一步看,随着处理器速度的增加,纹波噪声也会由于更多的逻辑状态吸收电流而相应的大量增加。

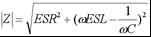

随着电路系统时钟频率的增加,很多情况就不能按照理想的电容器来考虑了。一个实际的电容不论是陶瓷电容还是电解电容,都可以被简化成一个串联RLC的模型。一个电容模型包括自身的电容C,还包括了等效的串联电感 ESL 和等效串联电阻ESR这两个重要的参数。这个串联模型的阻抗幅值是:

(3)

(3)

投稿箱:

电子变压器、电感器、磁性材料等磁电元件相关的行业、企业新闻稿件需要发表,或进行资讯合作,欢迎联系本网编辑部QQ:

, 邮箱:

info%ett-cn.com (%替换成@)。