PCB DFM的上述发展趋势并非独有,在目前的制造水平下,IC行业在整合软件技术与先进制造技术的过程中,也遇到了类似的挑战。比如Behrooz Zahiri在Chip Design Magazine (June/July 2006) 一篇文章中提到的:

“为了使用有效的DFM/DFY解决方案,IC设计者必须要能够处理系统失效或随机失效引起的制造问题。不幸的是,对于90nm及其以下的制程,现有的设计流程不能充分的处理这些DFM或DFY问题。”

“我们需要一个设计流程,在这个流程中,所有的设计和分析引擎都能够即时预知当前的设计在DFM/DFY方面 的表现。”

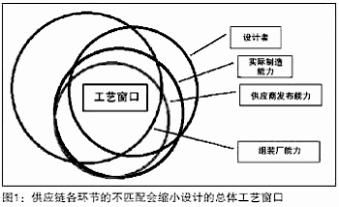

Zahiri继续写道:在过去,设计和制造是隔离的;但是现在,尽管工厂会提供设计规范给设计者,但是设计者仍然被错综复杂的制造问题所困扰。在早期,设计者可以认为:如果他们的设计严格遵守了厂家的DFM设计规范时,他们的芯片就能够生产出来,任何生产问题都可以认为是工厂的责任,并通过改善制程能力或更严格地控制制程来解决。其实,这种规范本身往往并不能完全真实地反映制造过程2。

随着IC设计者和软件开发者继续推动IC设计检查能力,制造知识与设计流程融合得更深了,PCB设计者也面 临相似的需求和压力。由于层数的增加、线间距的减小、更复杂的封装(小的表面贴装器件,BGA等等),制造问题的交互影响现在非常重要,需要细致的设计规划和预测能力,来保证生产出合格的产品。Zahari的文章指出了PCBDFM/DFY下一阶段的前进方向。

因此,我们先花点儿时间来看看我们该怎样达到这一点,这样我们可以获得对前途更透彻的观察。

DFM——电子设计自动化的时宜选择

PCB设计检查工具在20世纪80年代早期就已出现,而IC设计检查工具的根源可以追溯到20世纪70年代晚期和80年代,早期被非R&D设计团队使用。由于IC设计和PCB设计之间的紧密关系,两种设计软件的发展趋势比较相似,虽然大多数创新都产生于IC设计行业,然后传播到PCB设计行业。

DFM错误类型DFM问题通常表示为如下表所示一个2×2的矩阵:

● 灾难性的——板设计不能实现期望的功能

● 参数化的——板可实现功能,但并非在所有规格下都 能实现

● 系统的——不能一致、平稳地运行预先设计的功能

● 统计的——从表面上看随机或与其它条件没有关联的失效。

DFY的设计一般聚焦于统计性的错误,DFM一般聚焦于系统性的错误,而DRC倾向聚焦于识别系统的/灾难性的错误。

影响DFM设计工具发展趋势的因素