[发布时间]:2015年6月24日

[来源]:DIGITIMES

[点击率]:2385

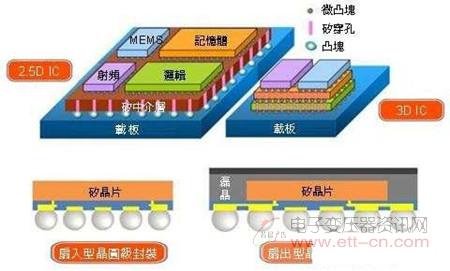

系统级封装(System in Package;SiP)结合内嵌式(Embedded)印刷电路板(Printed Circuit Board;PCB)技术虽符合移动设备小型化需求,然于供应链与成本存在问题,另一方面,扇出型晶圆级封装(Fan-out Wafer Level Package;FoWLP)不仅设计难度低于矽穿孔(Through Silicon Via;TSV) 3D IC,且接近2.5D IC概念与相对有助降低成本,可望成为先进封装技术的发展要点。

SiP可堆叠多颗芯片,搭配内嵌式PCB技术,将被动元件或无法SiP的芯片内嵌于PCB,再封装SiP于PCB上,将有利于设备缩减体积,然因PCB的配线密度低于芯片,在内嵌芯片于PCB前,尚需经过可增加接点(Pad) 间距的重新配置层(Re-Distribution Layer;RDL)制程,此造成供应链结构复杂,且一般PCB的制程良率约95%,采用内嵌式PCB技术,在PCB制程中5%的瑕疵品内将含有价格较高 的芯片,亦将在成本构造上产生问题。

另一方面,为增加芯片与载板、PCB间的I/O(输入/输出)数,TSV 3D IC的概念渐成形,然其设计难度高,因此出现2.5D IC,亦即在芯片与PCB间使用矽中介层(Interposer),再进行TSV,而由于2.5D IC相对TSV 3D IC不利于缩小体积,且存在TSV矽中介层成本甚高等问题,是以接近2.5D IC概念但有利于降低成本的FoWLP技术渐受重视。

DIGITIMES Research观察,FoWLP在比芯片更广的面积中构成凸块阵列(Bump Array),可对应配线密度较低的载板凸块接点尺寸与间距,因不使用既有打线,其内部连结较短,有利于缩减整体封装厚度,且未使用打线与中介层,亦有助 于降低成本,可望成为先进封装技术的发展要点。

2.5D/3D IC及扇入型/扇出型晶圆级封装比较

资料来源:NOVATI、SPTS、LIG投资证券,DIGITIMES整理,2015/5

投稿箱:

电子变压器、电感器、磁性材料等磁电元件相关的行业、企业新闻稿件需要发表,或进行资讯合作,欢迎联系本网编辑部QQ:

, 邮箱:

info%ett-cn.com (%替换成@)。