最近在美国加州召开的第八届国际互连技术年会受到了IC设计工程师前所未有的关注。传统上,这是一个针对在IC上创建互连堆栈的工艺工程师的高度专业论坛,今年的年会不仅吸引了规模超前的工艺工程师,而且还引起了芯片设计师的关注。

“互连尺寸缩小与晶体管尺寸缩小不同,”英特尔公司高级研究员Mark Bohr介绍道,“随着晶体管尺寸的缩小,它们的速度会变得更快。但互连却不是这样。当你减小互连线的宽度时,你必须同时减小厚度,以保证其阻抗不会下降。”

这一事实就是促使英特尔发展战略从追求更快单内核处理器芯片向多内核芯片转变的一个重要因素,Bohr指出。

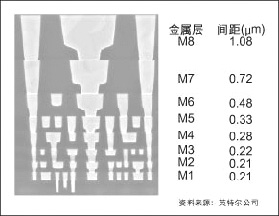

图1:65nm设计需要更加有效的工艺控制

在特许半导体公司从90nm向65nm互连转移的过程中,该公司战略联盟副总裁John Martin也认识到了这种问题,他把问题分成三类:布局布线、尺寸控制、以及芯片与封装的交互。其中布局布线可能是最重要的问题。

为了制造出那些更小晶体管所允诺的密度,采用65nm工艺的最初几个金属层必须允许非常小的金属间距。在90nm节点,Metal-1层上的间距首次变得如此细微,以致于必须采用光接近校正(OPC)才能正确修正Metal-1掩模上的图案。

在65nm节点,可能更多的金属层需要采用OPC技术。尽管供应商很难确定究竟哪些层需要OPC,但据Bohr透露,在英特尔的65nm工艺设计中,Metal-1到Metal-3都必须在193nm步进器上曝光,因此估计这些层都需要采用OPC。

“我们已经在OPC方面付出很多努力,以确保我们正在创建的特性尺寸正是设计师所希望的。”Martin说道,“对于1x层来说更是如此,因为这些层具有最精细的金属间距。”

那些需要采用OPC的层还要求工艺工程师、掩模制造商和芯片物理设计小组之间实现非常紧密的交互,这样才能确保设计师的意图能够在金属层中得以忠实体现。当OPC被限制在Metal-1层时,这仅仅意味着单元设计师必须与代工厂紧密合作,而并没有什么新意。但是当这种要求上升到互连堆栈时,那些只是对标准单元设计进行布局布线的IC设计师也将被牵涉进来,因为现有的布局布线工具很容易创建出与OPC不兼容的版图。

“眼下我们正处于一个临界点上,即由设计小组创建的金属层需要进行OPC兼容性检查。”Martin指出,“从某种角度看我们应该立即与设计小组展开紧密合作,以便创建可用来修正他们意图的掩模图案。”

这种密切合作的关系在另外一个检查领域-尺寸控制中早已存在,而且在65nm设计中这种关系会变得更加紧密。即使用光阻材料创建出正确的图案,在金属和绝缘材料中实际形成正确形状之前还有诸多问题需要解决。化学机械抛光即是问题之一。

旋转抛光盘、抛光材料以及晶圆表面之间的交互过程相当复杂,而且不幸的是,对于设计师来说这些都与图案非常相关。线条的走向和形状,尤其是它们的空间分布将决定抛光期间被去除的金属份量。

其它的变化来自于光刻工艺,其中焦点的变化会引起宽度变化;在沉积时,薄膜的厚度也会发生变化;在蚀刻过程中,当把抵抗层中的一个开口转变成基底材料中的沟道时可能引发进一步的变化。所有这些变化累积起来并转换成互连部分的阻抗和电容的变化。

“互连走线时延建模是个严重的问题,”Bohr指出,“现在我们已到了这么一个节点上,即我们需要采用更复杂的模型才能正确地反映出互连的期望形状,简单的集总模型已经无法做到这一点了。”但从65nm以后,这一问题将变得更糟。Bohr警告说,互连几何形状的变化正在接近被广泛讨论的晶体管参数变化的重要性。“现在已经无法进行最坏情况下的设计。现在IC设计师必须采用一些统计设计技术来计算晶体管的变化,否则会遗留很多问题,并最终产生不具竞争力的设计。”Bohr说道,“对于互连来说也将逐渐变得如此,不过65nm设计还没到这个地步。”

之所以还没落到这种地步,原因之一是由于部分工艺集成工程师付出了不懈努力。例如,英特尔成功地解决了过孔形成方面的问题,现在其设计规则不要求在信号路径中设置冗余的过孔。“有许多事情可以做,例如用铜箔填充过孔、正确设置屏障等,这都有助于解决过孔形成问题。”Bohr表示。

特许半导体公司及其工艺开发合作伙伴IBM、英飞凌和三星公司正在尺寸变化方面开展相似的工作。“一个重大因素是特许半导体已从AMD获得了自动精确制造(APM)工艺控制系统的许可。”Martin透露,“APM的特点之一是抛光工艺以及控制它能创建的可变性。迄今为止,我们的数据表明APM在我们的代工环境和AMD的批量生产环境中都是有效的。“但另一个重要部分是,”Martin补充道,“可以和设计小组协作控制整个裸片上的图案密度,从而使抛光机能够工作在一个相对统一的表面上。”

再来看看65nm以下的设计,其发展路线还不太清晰。随着金属尺寸的缩减,减小绝缘材料的介电常数将至关重要。但Bohr表示,至今介电常数k只有很小的进展。“我们改到低k值的蚀刻终止层,这将有助于整个堆栈的k值效应。”他指出,“不过目前减少走线间电容的最佳途径是增加金属层以减少拥塞。但我们不能一直这样做。”

“我期待在做45nm设计时,我们能选择到一种合适的新型绝缘材料。”Martin说,“目前还没有65nm适用的具有合适的机械和工艺集成特性的材料。”

现在的候选材料仍有问题。“薄膜中的铜(例如较低金属层)很不牢固,”非接触抛光供应商ACM Research公司总裁兼首席执行官David Wang认为,“今天我们之所以能够使用机械抛光法是因为很薄的金属条可以获得垫在它们下面的绝缘材料的机械支撑。铜的Young氏系数约为40左右。而新的低k材料Young氏系数约为3,它们不再支持铜。如果采用机械抛光而又不够小心的话,很容易超出这种材料的弹性限度而使其受损变形。”

65nm设计仍可保持乐观,与90nm工艺相比,几乎没有材料上的变化(特许半导体公司的情况更是一点也没变)。但是65nm设计仍需要更加有效的工艺控制,以及与设计团队更为紧密的合作关系。而45nm还存在许多悬而未决的问题。不过,没有人能够再认为互连问题不需要加以特别关注了。