AMD CTO Mark Papermaster讲解了Steamroller(压路机)架构之后,Jeff Rupley也公开了Bobcat(山猫)架构继任者Jaguar(美洲豹)的详情。如果说推土机主攻的还是AMD的主业---传统处理器,而山猫、美洲豹则是轻量级的便携市场,但是前途无量。来看超能网的解析:

美洲豹架构用于2013年的低功耗APU产品中,主要是双核的Tamesh APU以及双核、四核的Kabini APU中,他们的GPU也会升级到GCN架构。

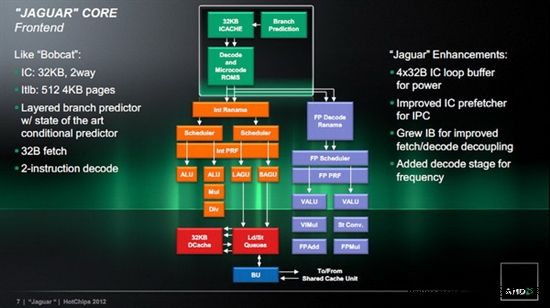

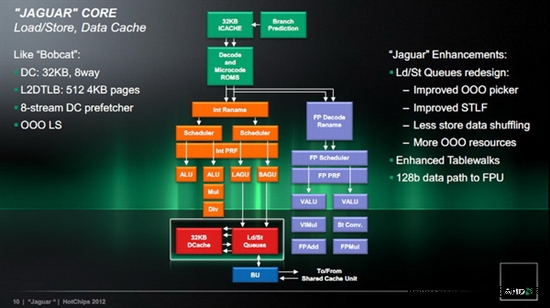

美洲豹的架构体系与Bobcat类似,不同于Atom使用顺序指令架构(in order),AMD的低功耗产品也坚持使用乱序指令体系(out of order),前者的结构简单,但是后者的性能更强。

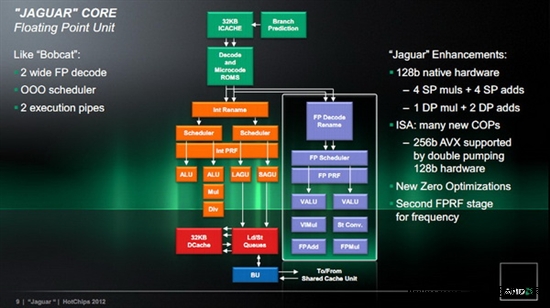

此外,美洲豹也要与时俱进,支持SSE 4.1、SSE 4.2、AVX及AES指令,同时还支持虚拟化功能,不过这一点没有具体细节。

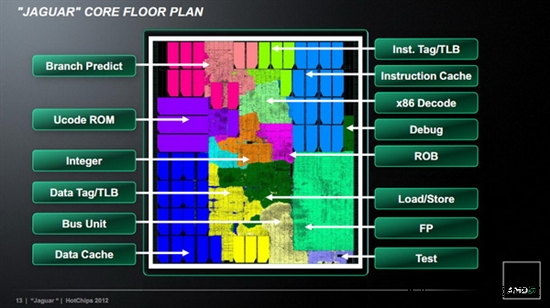

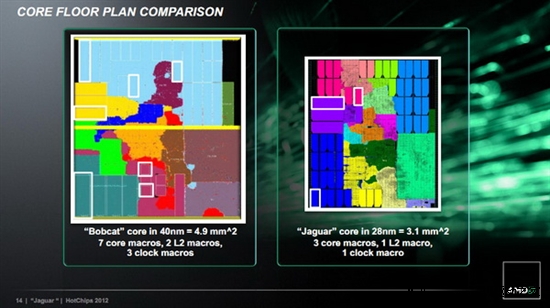

美洲豹将使用28nm工艺制造,每个内核的面积只有3.1mm2,而Bobca使用40nm工艺制造,每个内核面积有4.9mm2。

前端部分与Bobcat的结构大部分相同,都是2路32KB指令缓存,512 4KB页面,2发射解码,但是美洲豹做了增强,改进了IC预取器,提升了性能。

整个架构最大的变化是增加了硬件除法器(Hardware divider),这也是Llano所不具备的功能。

浮点单元部分依然是2条执行管线,乱序指令调度,但是原生128bit浮点单元现在可以执行更复杂的操作,并通过加倍dumping支持256bit AVX指令。

另外,L1数据缓存还是32KB,但是AMD做了存储/载入优化,现在它也可以通过128bit通道连接浮点单元。

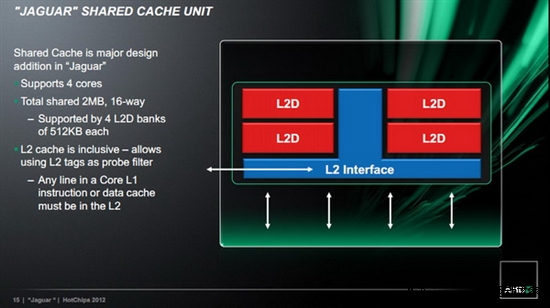

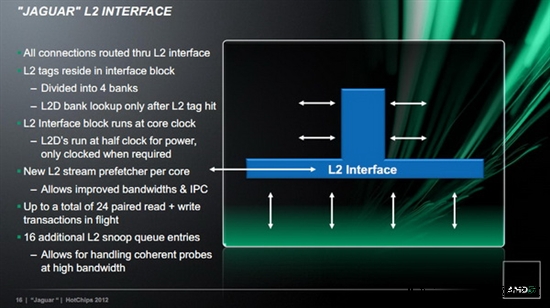

L2缓存部分AMD也做了较大调整,这也是与Bobcat架构区别较大的地方。2MB缓存被一条L2界面分成4部分512KB的区块,每部分L2D都是独占的,这一设计其实跟刚刚介绍过的Steamroller架构的动态L2缓存差不多,以1/4隔断按需分配L2缓存,不用的就可以关闭以节省能耗,主要目的就是省电,特别是对美洲豹这样面向便携平台设计的处理器来说,节能降耗对提升续航意义重大。

另外,为了节能AMD还为美洲豹的每个内核增加了C6状态,可以独立启用或者关闭。

至于性能提升,AMD称IPC(每周期指令)性能提升了15%,其中频率提升贡献了10%,换句话说架构设计带来的性能提升微乎其微,美洲豹的目标应该集中在升级制程,降低功耗,提升续航,减少核心面积等方面,反正性能也不是这类处理器的主要出发点。

美洲豹处理器将在明年发布,不过Intel明年也会发布22nm工艺的新一代Atom处理器Valleyview,后者在制程上及SOC上很有优势,二者的遭遇战又会如何呢?